高性能仿真器

文章类别:

快捷索引

未通过安全和安装测试,使用后果自负与本论坛无关

软件版权归原作者及原软件公司所有,如果你喜欢,请购买正版软件

注:此链接下载转自:TLF论坛

Super-FinSim是顶级的线性FinSim Verilog仿真器,从1993年放出第一款FinSim Verilog仿真器至今,FinSim Verilog已经引入了许多崭新的功能:混合编译和解释型仿真,仿真工厂可以让工程师管理数以百计的同步仿真、分离和增量编译、高性能保存和重启、直接集成C代码,无须PLI。

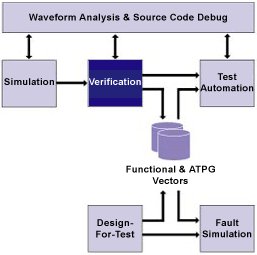

Super-FinSim 仿真环境由一个附带OVI的Virology编译器,一个仿真构件和一个仿真内核组成。Verilog编译器用于(1)检查设计的句法和语意的正确性,(2)依据设计要求产生配置仿真内核所要求的代码和数据。(3)选择性的产生一个供其它应用程序处理的中间格式表达。仿真构件用于链接构成一个仿真器所需要的所有文件,例如,编译器的输出和仿真内核。主C链接器用于此目的。仿真内核是所有Veilog设计仿真公共代码。一旦配置完成,仿真内核就成为一个定制的Verilog设计的仿真器。Super-FinSim的仿真器可以运行

Super-FinSim Verilog 编译器有一个快速和强大的能进行广泛错误检查和恢复的分析器。此外,分析器能产生标明潜在设计错误的警告信息代码,例如,交换一个越界的数组元素。

Super-FinSim Verilog 编译器支持来自Verilog-XL的一些编译器选项,包括控制库搜索功能的选项。为便于引用命令文件同样得到支持。必需事先指定希望的Super-FinSim 仿真器模式,不管是编译,解释或编译、解释的混合状态。如果不指定,Super-FinSim将会试图仿真编译模式下的整个设计,如果发现了一个许可的编译仿真器,否则,将在解释模式仿真设计。所有的编译信息储存在登记文件‘finvc.log’。

Super-FinSim仿真器使用仿真内核的波形例程接口支持实时波形显示。最近的Super-FinSim从数据I/O的工程捕捉系统(ECS)和Veribest’s Veriscope支持实时波形显示。用ECS波形显示构造仿真器,必须指定选项‘-ecs’。用Veriscope波形显示构造仿真器,必须指定选项‘-veriscope’。

以上图片文字概述来自E维软件资讯网

高性能仿真器 → https://www.books51.com/303602.html |

下一篇: 首席建筑师V10.07

最新评论